Tech Papers

Optimizing BSI Sensor Yields With Integrated Production Services

Category: BSI Sensors

This paper discusses an innovative manufacturing process that enables the production of back side illumination (BSI) sensors, driving improvements in high-speed imaging. Because high frame rates are accompanied by small resolutions, it can be a challenge to see the subject matter.

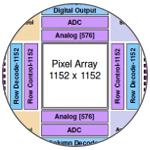

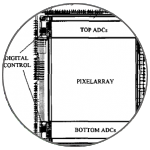

133 MPixel 60 fps CMOS Image Sensor with 32-Column Shared High-Speed Column-Parallel SAR ADCs

Category: CMOS Image Sensor

To realize next-generation highly realistic sensation broadcasting systems, the research and development of 8K ultrahigh-definition television (UHDTV) systems have been promoted. To realize 8K video cameras, 33Mpixel sensors [1-2] and a full-resolution camera system that uses three 33Mpixel sensors [3] have been reported.

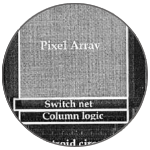

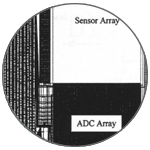

A 4-Side Tileable Back Illuminated 3D-Integrated Mpixel CMOS Image Sensor

Category: CMOS Image Sensor

The dominant trend with conventional image sensors is toward scaled-down pixel sizes to increase spatial resolution and decrease chip size and cost [1]. While highly capable chips, these monolithic image sensors devote substantial perimeter area to signal acquisition and control circuitry and trade off pixel complexity for fill factor.

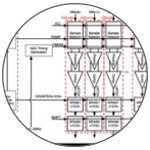

High Frame-Rate Global Shutter Image Sensor with Dual-Reset Branch SAR ADC Architecture

Category: CMOS Image Sensor

This paper describes a high-speed 1.3 Mpix global shutter CMOS image sensor with a column parallel SAR ADC readout. In order to achieve the row time requirements at the maximum frame rate, the SAR ADC utilizes a novel dual reset branch architecture.

BSI Low Light Level CMOS Image Sensor Employing P-type Pixel

Category: CMOS Image Sensor

A backside illuminated (BSI) CMOS imager technology optimized for night vision applications (NVCMOSTM) has been developed employing a hole-based p-type pixel (pMOS). Benefits of the technology include lower dark current and reduced random telegraph noise (RTN) as compared to conventional electron-based n-type pixels (nMOS).

Real-time Calibration of a 14-Bit Single Slope ADC with 290 MHz On-chip Accelerated Ramp Generator for Column-Parallel Image Sensors

Category: ADC and DAC Converters

This paper presents a real-time calibration scheme for a 14-bit multi-segment, single slope ADC architecture using a 290 MHz current DAC based on-chip ramp generator. The ramp generator enables the creation of a ramp with multiple slopes, allowing scaling of the ADC resolution according to a given system’s shot noise limited curve.

RF Design Issues and Challenges in a CMOS Image Sensor Process

Category: CMOS Image Sensor

This paper presents design issues and challenges encountered when designing RF transceiver circuits in a 0.18 µm 3.3 V/1.8 V CMOS Image Sensor (CIS) process. Even before putting down a transistor to design, there are infrastructure challenges to overcome.

Design of Analog Readout Circuitry with Front-end Multiplexing for Column Parallel Image Sensors

Category: CMOS Image Sensor

This paper reports progress in our column parallel analog signal chain design strategy, utilizing varying degrees of parallelism for CMOS image sensors. In [1] we investigated the trade-offs for different choices of parallelism and presented an analytical model for optimization of an endoscopic sensor.

Single Slope ADC with On-chip Accelerated Continuous-time Differential Ramp Generator for Low Noise Column-Parallel CMOS Image Sensor

Category: ADC and DAC Converters

This paper presents a 12-bit single slope ADC architecture that uses an on-chip ramp generator for low noise column-parallel CMOS image sensor. An on-chip continuous-time ramp generator is used instead of a discrete-time implementation.

Design of a PTC-Inspired Segmented ADC for High-Speed Column-Parallel CMOS Image Sensor

Category: ADC and DAC Converters

This paper presents a successive approximation ADC (SAR) architecture that takes advantage of the signal-dependent photon shot-noise characteristic of an image sensor. The multi-segmented successive approximation ADC (MS-SAR) applies the sub-ranging technique, where each segment’s conversion step size is scaled according to the photon transfer curve (PTC) of a given pixel.

A 2.5 inch, 33 Mpixel, 60 fps CMOS Image Sensor for UHDTV Application

Category: CMOS Image Sensor

We have developed a 7840 x 4360 pixel, 60 fps CMOS image sensor fabricated in 0.18 µm 1P4M process that is used for an Ultra High Definition Television (UHDTV) camera system.

Analysis and Simulation of CTIA-based Pixel Reset Noise

Category: Infrared Readout IC

This paper describes an approach for accurately simulating the reset noise of CTIA-based pixels. Using a circuit simulator to find the reset noise of a CTIA based pixel is not straightforward, due to the noise sampling and charge redistribution after the reset switch opens.

CMOS Integration of Capacitive, Optical, and Electrical Interconnects

Category: High-Speed Data Transport

We present a 90 nm test chip integrating proximity communication, optics using external lasers and photodiodes, and CML electronics on a single CMOS chip which can route data at multi-Gb/s rates through any combination of its three interconnect interfaces.

CMOS lmager with Embedded Analog Early Image Processor

Category: CMOS Image Sensor

We present a high quality computational CMOS imager with integrated early image processing general-purpose filter. The early processor identifies in real-time areas of interest within the field of view, and reduces data volume and data-bandwidth to the external processor.

Optical Transceiver Chips Based on Co-Integration of Capacitively Coupled Proximity Interconnects and VCSELs

Category: High-Speed Data Transport

Combining the strengths of both proximity communication and optical communication, a new hybrid input–output (I/O) platform delivers on-chip bandwidth off-chip and over distance. We demonstrate, for the first time, a four-channel hybrid I/O interface by integrating proximity communication and vertical-cavity surface-emitting-laser-based parallel optical interconnects on the same commercial 90-nm complementary metal–oxide–semiconductor platform.

A Low Phase Noise 10 GHz Optoelectronic RF Oscillator Implemented Using CMOS Photonics

Category: Analog and Mixed-Signal

The emerging wireless communications standards at higher frequencies, especially toward 60 and 80 GHz, are challenged by the availability of cost-effective high performance oscillators. Since the bandwidth of a wireless communications system is heavily dependent on the phase noise of the local oscillator, spectral efficiency at these frequencies is limited to a fraction of that achieved in cellular, WiFi, and WiMax applications.

Ultra High Light Shutter Rejection Ratio Snapshot Pixel Image Sensor ASIC for Pattern Recognition

Category: CMOS Image Sensor

The ultra high light shutter rejection ratio snapshot pixel image sensor ASIC is designed for detecting moving objects without motion artifacts. This chip can be integrated into the fast moving pattern recognition system, such as machine vision and robot control system.

A Two-Dimensional Array Imager Demonstrating Active Reset Suppression of kTC-Noise

Category: CMOS Image Sensor

The design and performance of a two-dimensional photodiode visible imager with a means of reducing the reset noise below the kTC limit is discussed. This active reset scheme uses feedback with an opamp per column in order to increase the gain and therefore the noise reduction over that seen for ordinary “soft” or “flushed” reset.

A Smart CMOS Imager with On-Chip High-Speed Windowed Centroiding Capability

Category: CMOS Image Sensor

Low-power, high-speed, accurate computation of centroid from a pre-defined window in the image plane is important for a number of space-based and commercial applications. These include object tracking in robotic systems, autonomous navigation, image compression, and document copyright protection, and much more.

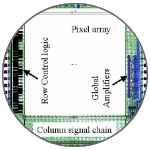

A High Speed, 240 Frame/s, 4 Megapixel CMOS Sensor

Category: CMOS Image Sensor

The paper describes a large format 4 Megapixel (2352 x 1728) sensor with on-chip parallel 10 bit ADCs. The chip size is 20 x 20 mm with 7 μm pixel pitch.The paper describes a large format 4 Megapixel (2352 x 1728) sensor with on-chip parallel 10 bit ADCs. The chip size is 20 x 20 mm with 7 μm pixel pitch. It achieves a high frame rate of 240 frames/s delivering 9.75 Gbit of data per second.

Dynamically Reconfigurable Imager for Real-Time Staring Vision Systems

Category: CMOS Image Sensor

Design and characterization of a high-performance multi-acuity, multi-window dynamically reconfigurable vision (DRV) CMOS imager for real-time staring vision systems is presented. By carrying out on-focal-plane image preprocessing, the imager chip simultaneously supports low-resolution large field-of-view (FOV) scan and high-resolution narrow FOV tracking.

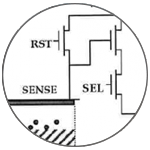

Analysis and Enhancement of Low-Light-Level Performance of Photodiode-Type CMOS Active Pixel Imagers Operated with Sub-Threshold Reset

Category: CMOS Image Sensor

Noise in photodiode-type CMOS active pixel sensors (APS) is primarily due to the reset (kTC) noise at the sense node [1], since it is difficult to implement in-pixel correlated double sampling for a 2-D array.

CMOS Sum & Difference Imager with On-Chip Charge-Leakage Compensation

Category: CMOS Image Sensor

This paper presents a new technique for implementing a low-power CMOS imager with simultaneous on-chip computation of the difference and sum of two successive frames. Existing difference imagers are susceptible to errors due to collection (by the sense element and in-pixel storage node) of photo-generated charge that diffuses from the photo-active pixel area during integration of the second frame.

A Low-Light to Sunlight, 60 Frames/s, 80 kpixel CMOS APS Camera-on-a-Chip with 8b Digital Output

Category: CMOS Image Sensor

In the last several years, many CMOS APS photodiode image sensors have been developed for consumer and commercial use. These sensors typically rely on illumination levels on the order of 100 Lux (a well-lit room) for optimal operation at video frame rates.

A High Speed, 500 Frames/s, 1024 x 1024 CMOS Active Pixel Sensor

Category: CMOS Image Sensor

The paper presents a high-speed (500 f/s) large-format 1K x 1K 8 bit 3.3V CMOS active pixel sensor (APS) with 1024 ADCs integrated on chip. The sensor achieves an extremely high output data rate of over 500 Mbytes per second and a low power dissipation of 350 mW at the 66 MHz master clock rate.

A Single Chip CMOS APS Digital Camera

Category: CMOS Image Sensor

There is an enormous demand for low power, highly integrated image sensor systems. CMOS based Active Pixel Sensor (APS) technology enables this progression. We demonstrate a very low power, highly integrated, programmable, complete digital camera-on-a-chip based on CMOS APS technology.

Megapixel CMOS APS with Analog and Digital Readout

Category: CMOS Image Sensor

This paper reports the operation and performance of two 1024 x 1024-element CMOS active pixel image sensors (APS) with on-chip analog-to-digital conversion (ADC), analog and digital readout signal chain electronics. Previously, a 256 x 256-element CMOS APS with on chip timing and control was demonstrated by JPL with excellent image quality.

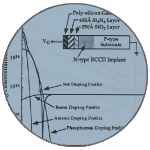

Simulation of High Density CCD Imager Structures

Category: CMOS Image Sensor

Simulation results are presented for design of high-density imager in the form of 3-phase BCCD with three layers of polysilicon gates. To assure a high charge transfer efficiency we have considered a process with a dual gate dielectric having 350Å Si02 layer covered with 650Å Si3N4 layer.