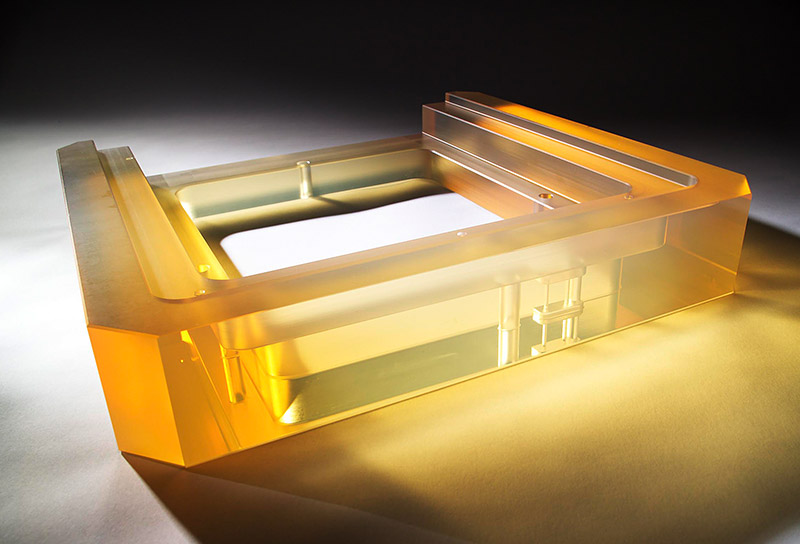

LIDAR ASIC with SPAD Based Pixel Array

Process/Specialty

- Pixel Process Simulation: Synopsys Sentaurus TCAD

- IR Drop Analysis: Silicon Frontline P2P Resistance Analysis

- Version Control: ICManage (fully integrated into design database tool flow)

- Quality Control & Certifications: ISO 9001:2015 Certification, ITAR DDTC Registered

Process/Specialty

- 4 MP array resolution

- 10.8 µm square pixels

- Lateral Overflow pixel architecture for high intra-scenic dynamic range

- 180 FPS at full resolution

- On-chip ADCs, PLL and temperature sensor

- 800 Mbps LVDS digital outputs

- TSMC 110nm Backside Illuminated (BSI) CIS process

en